単純な配列のアクセスの場合は、連続したアドレスの要素をアクセスする基本形のロードストア命令で良いが、ばらばらのアドレスのアクセスが必要とされる場合も多い。このようなケースでは、従来はSIMDではない1要素のロードストア命令を必要な回数だけ使わざるを得なかったが、間接ロードストア命令のサポートで、プログラムが簡単になり、次の図に示すように、ストアは1.67倍、ロードは1.92倍に性能も向上している。

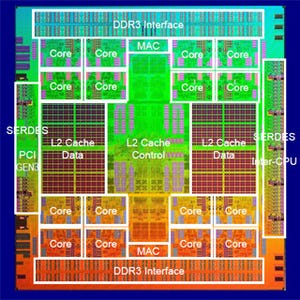

SPARC64 XIfxは34コアのプロセサであるが、次の図に示すように、17コアのCMG(Core Memory Group)が2つ接続された構成になっている。

ちょうど、2個の17コアのチップをIntelのQPIでつないだような形である。しかし、SPARC64 XIfxの場合は、QPIではなく富士通独自のインタコネクトであり、接続がチップに内蔵されている点が異なる。

また、SPARC64 XIfxでは、演算性能が上がった分に比例して大量のデータの供給と格納が必要になる。このため、次の図のようにキャッシュ、メモリ、Tofu2のバンド幅が改善されている。Tofu2のバンド幅の向上は、4倍あまりという演算性能の向上には追い付いていないが、やむを得ないところであろう。

1次キャッシュは読み出しが140.8GB/s、書き込みが70.4GB/sのバンド幅で、L2キャッシュとのインタフェースは半分のバンド幅となっている。そして、SPARC64 XIfxでの大きな設計判断は、HMCの採用である。4個のHMCをCMGに接続する構成で、読み書きともに120GB/sという高いバンド幅を達成し、コアの演算性能の向上とほぼバランスするバンド幅性能となっている。バンド幅を上げるにはこのような3D実装のメモリを使わざるを得ないが、2GBの容量のHMCを使ってもCPUチップ全体で32GBのメインメモリ容量に制限されてしまうことになる。

そして、ノード間やストレージシステムを接続するTofu2は、リンクの転送速度を2.5倍に向上している。当然、SSDなどの高速ストレージを使うと予想されるが、容量の小さいメインメモリをどのようにして補うかは注目したいところである。

HPCでは大量のデータを扱うが、これを次々とキャッシュに読み込んでいくと、キャッシュの容量を超えてしまい、本来はキャッシュに残っていて欲しいデータが上書きされて消えてしまう。これを避けるため、京コンピュータのプロセサでは消えては困るデータを入れる部分と、次々と新しいデータを入れて上書きされても良い部分の分離するセクタキャッシュという方式を考案して、実装している。

SPARC64 XIfxでは、これを拡張して4つのセクタを持つ構造とし、1セクタをアシスタントコアに割り当てている。このようにすることで、アシスタントコアの動作で、計算コアが使うキャッシュの内容が汚されてしまうことを防ぐことができる。

スパコンの計算では、多数の計算ノードに処理を分散するが、長い間、それぞれのノードが独立に計算していれば良いというは少なく、各ノードが1ステップ分の短時間の処理を行い、全ノードの処理が終わったら、次のステップの処理に入るというような計算が一般的である。このような場合、1ノードでも処理が遅れると、残りのすべてのノードが待たされることになり、性能が低下してしまう。

通常のOSではタイマー割り込みや通信などに伴う割り込みが非同期に発生し、割り込みを処理するOSが動いているノードの計算時間が長くなってしまうということが起こる。この頻度が少なければ良いのであるが、数万ノードもあると、各ステップで、どれかのノードに割り込みが入り、全部のノードが待たされるということが頻繁に起きてしまう。このためにスパコンの処理時間が、遅い方にバラつくが、これをOSジッタと呼んでいる。

このOSジッタを減らす1つの方法は、計算ノードと通信処理などを行うノードを分離して、計算ノードに入る割り込みを極力少なくすることである。このため、京コンピュータでは16個の計算ノードに1個のIOノードを付加する構造になっている。

アシスタントコアは、このIOノードをCPUチップに内蔵したものと考えられる。ヘビーな計算処理を行うわけではないので、HPC-ACE2は不要であるが、そのために特別なコアを開発するのは手間が勿体無いので、SPARC64 XIfxでは、計算コアと同じコアを使っているという。

前世代の9fxの場合も、OSを改造して割り込みを減らし、IOノードを置いているが、それでも3000ノード以上になると、ジッタで5%程度性能が低下していたが、より密結合のアシスタントコアを置くことにより、ジッタの影響を0.5%程度に抑えている。

そして、ノードごとにOSを動かすという方式ではなく、単一のOSで計算コアとアシスタントコアを管理する構造として、メモリ管理のオーバヘッドを減らしているという。

前世代の9fxと9種類の実アプリケーションの実行性能を比較したものが次の図である。SPARC64 XIfxでは新命令の追加やマイクロアーキテクチャの改善により、性能が向上していることが分かる。

アプリケーションによって大きな性能向上の原因がHMCによるメモリバンド幅向上であったり、256bit幅のSIMDであったりと異なるが、これらのアプリの平均では、前世代の9fxと比べるとコアあたり1.7倍の性能となっている。

また、富士通の伝統である高信頼度設計はSPARC64 XIfxにも受け継がれており、次の図に示すように、チップのほぼ全域が1bitエラーの訂正が可能な緑色なっており、ごく一部が訂正は出来ないが検出は可能となっている。また、キャッシュの固定故障部分を動的に切り離し、性能は低下するものの動作を続けるCache Dynamic DegradationやTofu2の故障レーンを切り離す機能なども新たに実装されている。

SPARC64 XIfxでは、HMCの採用は大きな決断であるが、それ以外は、アッと驚くようなアーキテクチャ変更はない。しかし、手堅く100PFlopsを目指すというアプローチは評価できる。

今回は消費電力が発表されなかったが、このあたりがどのようになっているかで、Exa Flopsまで同様な改善の延長で伸ばせるのかが決まってくる。今後の富士通の技術開発がどのようになっていくのか目が離せないところである。