詳細説明その3 - 10年でHPCの主要な座に着いたIntel、この先の展開は?

午前中の最後のセッションは、Rajeeb Hazra氏(Photo51)による"High Performance Computing"であった。HPCは既に産業向けにも広く使われ始めており(Photo52)、ここから更に一歩進んでBig Dataから直接新しい知見を取り出そうという方向に来ている(Photo53)。色々な意味で敷居は高いものの、次第にHPCは企業に浸透しつつあり、重要なポジションを占めつつある。このIntelの普及をTop500で比較したのがこちら(Photo55)で、10年でIntelはHPCの主要なインフラの座に着いたことを改めて示した。

|

|

Photo52: モデリングの段階で様々なテストや確認を行なうことで、試作を飛ばせるという話。実際、部品の合い具合とか、空気抵抗などに関してはCADレベルやCFD(Computational Fluid Dynamics)でテストができてしまう。勿論安全性の確認テストもあるから、試作が完全にゼロというわけにはいかないのだが。 |

|

|

Photo53: 先ほどの話とも絡むが、このData Driven Modelの作り方が肝なのであって、広く利用できるModelが構築できるまで、猛烈な回数の分析のやり直しが必要であり、これが高速なHPCが必要となる大きなポイントである。 |

|

|

Photo54: 競合であるAMDが事実上脱落していることもあって、このマーケットにおけるIntelのMSS(Market Share Segment)は非常に高くなっている。もっとも、GPGPUが普及し始めるとこのあたりはまた変わってくるかもしれないが。 |

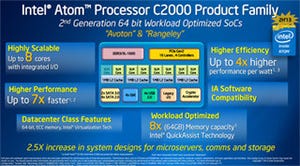

このマーケットに対してIntelはXeonやXeon Phi、10G Ethernetなどのソリューションと、これを支えるSoftware Building Blockは既に提供している訳だが(Photo56)、この先の展開として、Fabricをチップに統合するのがキーである、という見通しが示された(Photo57)。また今後の要素技術としては、FabricやSwitchに加え、次世代StorageやMemory Stacked CPUが示された(Photo58)。実のところIntelはNVIDIAなどと競いながら2020年に実現される(実際は2022年頃にSlipしそうだが)予定のExaflopマシンの開発に取り組んでおり、これに向かって開発を進める過程の要素技術がそのままHPC向けに落ちてくると考えれば良い(Photo59)。これらを盛り込みながら、引き続きIntelはHPCにAddressするという事をアピールした。

|

|

Photo56: InfiniBandなどに対して10GbEや、今後は先ほど出てきたSiPhなどが代替になってゆく、という風に考えているのだろう。もっともIntel自身も2012年1月にQlogicのInfiniBand部門を買収して居り、引き続きInfiniBandのソリューションも出してはいるのだが。 |

|

|

Photo59: Exaflopでは全体の消費電力を20MWに抑える必要があり、ここから逆算すると100GFlopsが2W程度で実現できないといけない。100GFlopsというのは、今で言えば例えばXeon E5-4607(2.2GHz駆動の6コア、TDP 95W)が105.6GFlopsだから、これを2Wまで落とすことになる。2Wまで落とせばMemory Stacked CPUは楽勝であろう。 |

次ページ:Breakout session