PCI-SIGは今年も恒例のPCI-SIG Developers Conferenceを6月25・26日のスケジュールでサンタクララで開催した。これにあわせてPress Conferenceが開催され、筆者も電話会議の形でこのPress Conferenceに参加したので、その内容をお届けしたい。

PCIe Going mobile

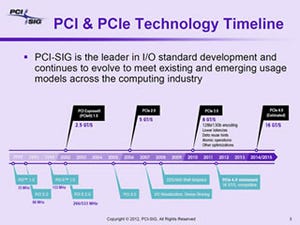

まずPhoto01が総論である。実は昨年からちょっとその傾向は見えたのだが、明確にMobile向けにシフトしていることが明らかにされた。今年のテーマは3つで、一つがMobile向けによりFocusすること、2つ目が(昨年も出てきた)OCuLink、3つ目がPCIe 3.1である。ということで以下各論。

まずはM-PCIeである。昨年のIDFの折に、PCI-SIGはMobile向けの方向性を明確に打ち出していた(Photo02)。で、具体的にこれをどう実現するかであるが、PCI-SIGはこうしたMobile向けに、MIPIのM-PHYを物理層として使うべくMIPI Allianceと共同で作業することを明らかにした(Photo03)。要するに物理層だけMIPIとするような仕組みである。メリットとして当時挙げられたのはこんな感じ(Photo04)。

|

|

Photo04: 例えば最近のSmartphoneには802.11acが搭載されているが、殆どのケースではPCIeではなくUSBの接続になっている。消費電力の観点ではともかく接続速度という観点ではUSBは決して賢明な方法ではないのだが、こうした部分をPCIeで置き換えたい、というのはPCI-SIGの意向だった。 |

で、これをどう実現するかであるが、Photo05の様にPHY Logicalの部分を入れ替えて、間にMIPI対応のブリッジに当たるものを挟み込む事で実現可能になるとしていた。御存知の方もおられようが、MIPIの場合速度とかはアプリケーションによって自由に変更できる。一方PCIeの方は速度は固定だし、そもそもその速度が高すぎるという問題があった。例えば先に例に挙げたIEEE802.11acの場合、1×1だと433Mbpsということになるから、まずはこれがターゲットになるが、PCIeはGen 1の1xでも2.5Gbpsで、必要とされる帯域の5倍も高速になる。MIPIだとこのあたり、もっと遅い速度を提供できるのだが、問題はPCIe側のProtocol Stackが2.5Gbpsを前提に記述されている事だ。このあたりをうまく調整するのが"Optimized PHY Logical"であり、Ramin Neshati氏はこれを"Glue Logic"と呼んでいた。

|

|

Photo05: M-PHYのSpecification自体は公開されていない(参加メンバーのみ)だが、仕様の概略はこちらに公開されている。 |

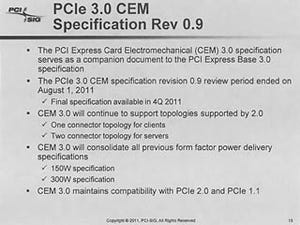

さてこの仕様、当時の予定ではECNの形でまずリリース、最終的にはPCIe 4.0でIncludeという事になっていた(Photo06)訳で、実際5月22日にM-PCIe ECNとしてリリースされたのだが、当初よりもう少し拡充されることになった(Photo07)。まずスピードとしては、Gear 1/2/3の3種類が定義されており、Gear 1/2がPCIe Gen1相当、Gear 3がPCIe Gen2相当になる。ちなみにAl Yanes氏によれば、将来的にはPCIe Gen3に相当するGear 4も予定しているとの事だった。このM-PCIeの位置づけは、先のPhoto05から変わっていない(Photo08)。

このM-PCIeの使われ方であるが、Photo09はMIPI Allianceが示しているM-PHYの適応図である。相対的に高速なI/FにM-PHYを、やや低速なI/FにD-PHYをそれぞれ利用するという構図を考えているようだ。今回のPCI-SIG DevConでは、Cadenceが後述するPCIe L1 PMのSolution以外にM-PCIeのコントローラをデモしたほかSynopsysがM-PHYとM-PICeコントローラIPのデモを行なった模様である。