Intelは、32nmのCMOSプロセスによるSoC(Sytem on a Chip)技術を開発し、2009年12月7~9日に米国で開催された電子デバイス技術に関する国際会議「IEDM2009」でその概要を発表した(講演番号28.1)。x86アーキテクチャのCPU「Atom」をコアとするスマートフォン向け次世代SoC「Medfield(開発コードネーム)」や組込機器向けSoCなどに応用するとみられる。

Intelは前年のIEDM2008で、45nmのCMOSプロセスによるSoC技術を発表済みである。45nmのSoCでは第1世代の高誘電率膜/金属ゲート(HKMG:High-k/Metal gate)技術を採用し、2種類のトランジスタを用意した。ロジック回路用と1.8Vの入出力用を兼ねるトランジスタと、3.3Vおよび5Vの入出力用トランジスタがある。

IEDM2009で発表された32nm世代のSoC技術は、第2世代の高誘電率膜/金属ゲート(HKMG)技術を採用し、3種類のトランジスタを用意した。ロジック用トランジスタ、低消費電力用トランジスタ、高電圧/入出力用トランジスタがある。

ロジック用トランジスタはHKMG技術を採用しており、高性能版(HP版)と標準性能/標準電力版(SP版)の2種類のオプションがある。HP版はゲート長が30nm、酸化膜換算のゲート絶縁膜厚は0.95nmで、電源電圧が1VのときにnMOSトランジスタが1.53mA/μm、pMOSトランジスタが1.23mA/μmの電流駆動能力(飽和ドレイン電流)を備える。オフ電流は100nA/μmとやや高い。SP版はゲート長が34nmとHP版よりも長い。酸化膜換算のゲート絶縁膜厚は0.95nmで、HP版と同じである。電流駆動能力は電源電圧が1VのときにnMOSトランジスタが1.12mA/μm、pMOSトランジスタが0.87mA/μmとHP版より下がる。その換わりに、オフ電流は1nA/μmと低い。

低消費電力用トランジスタもHKMG技術を採用する。酸化膜換算のゲート絶縁膜厚は0.95nmで、ロジック用トランジスタと共通のプロセスでゲート絶縁膜を形成している。ゲート長は46nmと長めになる。オフ電流は0.03nA/μmと非常に低い。ただし電流駆動能力はそれほど高くない。電源電圧が1VのときにnMOSトランジスタが0.71mA/μm、pMOSトランジスタが0.55mA/μmにとどまる。

高電圧/入出力用トランジスタは、ゲート絶縁膜の構造が違う。シリコン酸化膜と高誘電率膜の2層構造で耐圧を稼ぐ。1.8V入出力(1.8V版)と3.3V入出力(3.3V版)の2種類のオプションがあり、1.8V版はゲート長が140nm以上、酸化膜換算のゲート絶縁膜厚が約4nm、3.3V版はゲート長が320nm以上、酸化膜換算のゲート絶縁膜厚が約7nmとなっている。電流駆動能力は1.8V版のnMOSトランジスタが0.68mA/μm、pMOSトランジスタが0.59mA/μm(電源電圧1.8V)、3.3V版のnMOSトランジスタが0.7mA/μm、pMOSトランジスタが0.34mA/μm(電源電圧3.3V)。

これらのトランジスタとSoCの製造に使用する要素技術は、光源波長が193nmのArF液浸リソグラフィ技術、第4世代の歪みシリコン(sSi)技術、7層~11層の金属配線技術などである。

またアナログ回路および高周波回路の混載に向けた受動素子と能動素子を開発した。ウェル利用の抵抗素子、溝型コンタクト利用の抵抗素子、高精度抵抗素子(0.5%精度)、インダクタ素子(Q値は20以上)、金属フィンガー利用のキャパシタ素子、可変容量ダイオード(バラクタ)、縦型バイポーラトランジスタ、バンドギャップダイオード、高密度ヒューズなどがある。

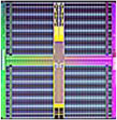

Intelは開発したSoC技術を利用し、291MビットのSRAMチップ(シリコンダイ)を試作して性能を評価した。HP版トランジスタを採用したときの動作周波数は3.8GHz、SP版トランジスタを採用したときの動作周波数は2.9GHz、低消費電力トランジスタを採用したときの動作周波数は2GHzに達した。いずれも電源電圧は1.1Vである。SRAMのセル面積は0.148平方ミクロン(高密度版)と0.171平方ミクロン(低電圧/高性能版)。

|

|

|

|

32nmのSoCプラットフォーム技術で試作した291MビットSRAMチップ(IEDMの論文集から抜粋) |

291MビットのSRAMチップによる動作周波数の評価結果(シュムープロット)(IEDMの論文集から抜粋) |

32nmの高性能CMOSロジックプロセスを改良

また同社は、前年のIEDM2008で発表した32nmの高性能CMOSロジックプロセスを改良した結果をIEDM2009で発表した(講演番号28.4)。

32nmの高性能CMOSロジックプロセスの要素技術は、ArF液浸リソグラフィ技術、第2世代のHKMG技術、第4世代のsSi技術、9層の金属配線技術などである。前年のIEDM2008で発表したトランジスタの電流駆動能力(飽和ドレイン電流)はnMOSトランジスタが1.55mA/μm、pMOSトランジスタが1.31mA/μmだった(電源電圧は1.0V、オフ電流は100nA/μm)。それぞれ45nm世代に比べて14%と22%、電流値が向上していた。

今回のIEDMで発表されたトランジスタの電流駆動能力はnMOSトランジスタが1.62mA/μm、pMOSトランジスタが1.37mA/μmである(電源電圧は1.0V、オフ電流はオフ電流は100nA/μm)。それぞれ前年の発表より、4.5%と4.6%、電流駆動能力が上昇した。

改良したトランジスタ技術でIntelは、3.25MビットのSRAMアレイと91MビットのSRAMアレイを試作してみせた。SRAMのセル面積は3種類あり、0.171平方ミクロン、0.199平方ミクロン、0.256平方ミクロンである。