HPC-ACE向けプロセッサの仕様を公開

富士通は2009年3月2日、同社WebサイトのHPC(科学技術計算・解析)のページに次期スパコン向けプロセッサの論理仕様書を公開した(注:PDF)。

このプロセッサの命令アーキテクチャはSPARCベースであるが、HPC向けに大幅に命令拡張が行われており、「HPC-ACE(High Performance Computing - Arithmetic Computational Extensions)」という名前が付けられている。

また、このプロセッサの正式名称は「SPARC64 VIII fx」である。現在、同社のSPARC Enterpriseサーバに使用されている4コアプロセッサは「SPARC64 VII」であるので、これの次世代にあたると考えられる。同社のWebサイトでは単にこのプロセッサを開発中と述べているだけで、このプロセッサが、何時ごろ、どのような製品に利用されるかなどについては何も書かれていないのであるが、8コアのHPC向けプロセッサとなれば、理化学研究所(理研)と開発を進めている10PFlopsの日の丸スパコンのプロセッサであることは間違いない。

とすると、第1次の部分稼動でも2010年度末の予定であり、まだ、2年も先のプロセッサの詳細な論理仕様を公開するというのは、プロセッサ関係の技術情報を多く公開している富士通としても異例に早い時期の公表である。やはり、次期スパコン用のソフトウェアの開発には時間が掛かるので、早期に公表する方が良いと判断したのであろう。

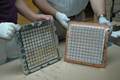

このSPARC64 VIII fxプロセッサであるが、昨年8月のHotChipsでの同社の丸山氏の発表の最後で触れられた「Venus」という開発コードネームのプロセッサと考えられる。この発表資料では、富士通の45nm CMOSプロセスで作られる8コアプロセッサであり、チップの性能は128GFlopsとなっている。

これらの情報を総合すると、SPARC64 VIII fx は、SPARC V9アーキテクチャをHPC向けに大幅に強化したHPC-ACEコアを8個集積し、メモリコントローラを内蔵したプロセッサであり、各コアは4つのFMAユニットを搭載し、倍精度の浮動小数点演算を、8演算/サイクルで実行できる。また、1サイクルあたりの浮動書数点演算数は64であるので、128GFlopsということは、クロック周波数は2GHzとなる。

そしてプロセッサコアは16段のパイプライン構成であり、各コアは32KBの1次命令キャッシュ、32KBの1次データキャッシュを持ち、8コア共通の5MBの2次キャッシュを搭載している。

このSPARC64 VIII fxの1サイクル当たりの倍精度浮動小数点演算数としては、Intelの次世代NehalemであるSandy Bridgeで実装予定のAVXと同等である。ということで、メモリコントローラの内蔵とあわせて、Sandy Bridgeと非常に近い機能のチップであるが、類似はここまでである。

AVXは従来128ビット幅であったSSE2を256ビット幅に拡張している。したがって、1つの命令で4つの64ビットの倍精度浮動小数点演算を実行することができる。そして、浮動小数点加算器(FA)と浮動小数点乗算器(FM)を持っているので、一方が加算で他方が乗算であればそれらの2命令を1サイクルに並列実行できる。

一方、SPARC64 VIII fxは、2つの浮動小数点積和演算を実行する従来のSPARC64プロセッサを拡張し、それぞれのFMA命令が1組のデータの演算を行うのではなく、BasicとExtendedと呼ぶ2組の演算器でデータを並列に演算する構造になっている。

FMA演算器はA*B+Cを計算するが、A*Bの結果は110ビット程度の長いままで保持して次の加算を行うので、乗算と加算を別々に行うAVXのような実装よりも計算誤差が小さいというメリットがある。