さて、次からがNehalemである。Photo02では"Nehalem"の文字の下に、1~8coreまでScalabilityがあるとしているが、7 coreといった普通はありえない構成をアーキテクチャ的にサポートしていることが明確にしめされた。まぁそれはともかく、「さて、8core製品の構成は?」というのが疑問である。Intelは今のところ、2008年にリリースされるQuad Core製品がSingle Dieであるということは事実上明らかにされているが、2009年にリリース予定の8coreについては、まだ詳細が明らかになっていない。選択肢は2つあり、

- Native 8core。つまり1ダイの上に8coreが集積される

- Quad Core MCM。つまり2つのQuad Coreのダイがチップ上で密結合

のどちらかとなる。ただ、Native 8coreは少なくともNehalem(つまり45nmプロセス)ではありえない、というのが筆者の予想だ。

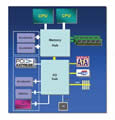

もう少し具体的にみてみよう。Nehalemのダイ写真を元に、内部構成を推定してみたのがPhoto03だ。ダイ寸法が20mm×13.6mmと仮定すると、Photo03におけるCPU Core1つあたりのサイズはおおよそ4.1mm×7.7mmで31.6平方mmという計算になる。これが4つで126.4平方mmだ。これをPhoto01と見比べると、CPUコアだけでPenrynのダイサイズよりも大きいわけである。仮にL3 CacheとかMemory I/F、Quick Path I/Fなどを一切変えずに8coreを作ったとしても、398.4平方mmに肥大化することになる。殆どItanium 2並のサイズである。実際にはL3のサイズが同じではボトルネックになりそうだから、多少なりとも強化する必要がある。L3 Cache+L3 TagRAMのサイズはおおよそ18.2mm×4.3mmで78.3平方mmほど。倍増とは言わないまでも1.5倍に増やすと、コア全体のサイズは437.6平方mmと史上最大に膨れ上がる。いくらなんでもこれは考えにくいところだ。AMDのTricoreについて、「それはYield(が低くてQuad Coreとして出せない)の問題であり、我々にはそうした問題はない」とGelsinger氏やStephen L. Smith氏(Vice President, Director, Digital Enterprise Group Operations)は口を揃えるが、このダイサイズではIntelも6coreとか7core製品をラインナップに用意せざるを得ないかもしれない。

これが解決するのはいつか、というと恐らくは32nm世代だ。Tick-Tockモデルで言うところのTick、つまり同じNehalem Microarchitectureを継承しつつ32nmプロセスを使うWestmereが2009年の登場を予定している。プロセスの微細化でほぼダイサイズは半減するから、45nmでは437.6平方mmと巨大なダイであっても、32nmならば230平方mm前後に落ち着くだろう。L3 Cacheを増やしても、Nehalemより小さなダイにすることは難しくなさそうだ。原価を考えても、45nm世代で8coreを製造するのはかなり無理があると思う。